### UNIVERSITY OF NORTH BENGAL

B.Sc. Honours 3rd Semester Examination, 2023

# **CC7-PHYSICS**

# **DIGITAL SYSTEMS AND APPLICATIONS**

Time Allotted: 2 Hours Full Marks: 40

The figures in the margin indicate full marks.

#### **GROUP-A**

| 1. | Answer any <i>five</i> questions from following: | $1 \times 5 = 5$ |

|----|--------------------------------------------------|------------------|

|    |                                                  |                  |

(a) Choose the correct answer:

For a logical circuit there are n binary inputs. Then the number of different input combinations in the truth table is

- (i) 2n (ii) 2/n (iii)  $2^n$  (iv) 2(n+1)

- (b) In an Even parity scheme, which of the following words contain an error? Explain.

- (i) 10110111 (ii

- (ii) 11101010

- (c) Convert (10011010101)<sub>2</sub> to Octal.

- (d) Subtract (1010)<sub>2</sub> from (1111)<sub>2</sub> using 2's complement scheme.

- (e) Using Boolean algebra, verify  $\overline{A}B(\overline{D} + \overline{C}D) + B(A + \overline{A}CD) = B$ .

- (f) Write down full form of ASCII.

- (g) What is the decimal number represented by the BCD code 101000111?

- (h) What is the minimum number of flip-flops required for a synchronous decade counter?

#### **GROUP-B**

## Answer any three questions from the following

$5 \times 3 = 15$

- 2. Draw the logic symbol of 4:1 DEMUX using basic gates. Write one application of multiplexer. 4+1

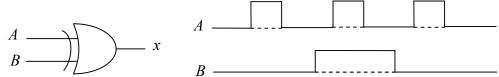

- 3. (a) Determine the output waveform x for the input waveforms A and B given below for a XOR gate. 2+3

- (b) Construct a Full Adder circuit using two Half adders and an OR gate and describe the operation.

- 4. (a) Derive the Boolean expression for a two input XOR gate to realize with two input NAND gates without using complemented variables and draw the circuit.

- (b) Simplify the Boolean expression  $(A+B)(\overline{A}+C)(\overline{B}+D)(C\overline{D})$ .

#### UG/CBCS/B.Sc./Hons./3rd Sem./Physics/PHYSCC7/2023

- 5. (a) Simplify the following expression using *K* map  $f(A, B, C) = \sum m(2, 3, 4, 5) + \sum d(6, 7)$

- (b) What do you mean by Minterm and Maxterm?

- 6. What is a parity checker? Discuss how XOR gate can be employed as parity checker. 1+4

### **GROUP-C**

# Answer any two questions from the following

$10 \times 2 = 20$

3+2

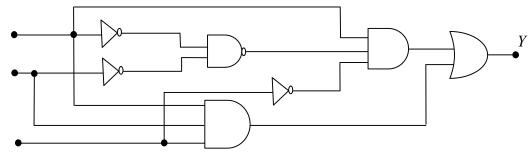

7. (a) Simplify the logic circuit given below and then implement the simplified circuit 4+4+2 with logic gates.

- (b) With the help of logic diagram and truth table, explain a 3-line to 8-line decoder.

- (c) Distinguish between an encoder and a decoder.

- 8. (a) What advantage does a J-K flip-flop have over S-R flip-flop?

2+5+(1+2)

- (b) Construct the logic diagram of a master-slave JK flip-flop and explain the working principle.

- (c) What is D flip-flop? Show how an S-R flip-flop can be converted into a D flip-flop.

- 9. (a) Explain the operation of 4-bit serial in parallel out shift register. Give some (4+2)+4 applications of shift register.

- (b) Construct Karnaugh map to design a logic circuit with minimum number of logic gates and implement the following truth table with logic circuit:

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

10.(a) Write short notes on any *two* of the following:

2+(1+4)+(1+2)

- (i) DRAM

- (ii) ALU

- (iii) CPU

- (iv) Mapping techniques.

- (b) Distinguish between synchronous and asynchronous counters. Describe with necessary diagrams the working of asynchronous counter.

- (c) What is multivibrator? Draw the circuit diagram of an astable multivibrator and explain its principle of operation.

\_\_\_\_×\_\_\_

2

3135